Chapman & Hall/CRC

Computational Science Series

## THE GREEN COMPUTING BOOK

Tackling Energy Efficiency at Large Scale

## Chapman & Hall/CRC Computational Science Series

#### SERIES EDITOR

#### Horst Simon

Deputy Director Lawrence Berkeley National Laboratory Berkeley, California, U.S.A.

#### **PUBLISHED TITLES**

COMBINATORIAL SCIENTIFIC COMPUTING Edited by Uwe Naumann and Olaf Schenk

CONTEMPORARY HIGH PERFORMANCE COMPUTING: FROM PETASCALE TOWARD EXASCALE Edited by Jeffrey S. Vetter

DATA-INTENSIVE SCIENCE

Edited by Terence Critchlow and Kerstin Kleese van Dam

PETASCALE COMPUTING: ALGORITHMS AND APPLICATIONS Edited by David A. Bader

FUNDAMENTALS OF MULTICORE SOFTWARE DEVELOPMENT Edited by Victor Pankratius, Ali-Reza Adl-Tabatabai, and Walter Tichy

THE GREEN COMPUTING BOOK: TACKLING ENERGY EFFICIENCY AT LARGE SCALE Edited by Wu-chun Feng

GRID COMPUTING: TECHNIQUES AND APPLICATIONS Barry Wilkinson

HIGH PERFORMANCE COMPUTING: PROGRAMMING AND APPLICATIONS John Levesque with Gene Wagenbreth

HIGH PERFORMANCE VISUALIZATION: ENABLING EXTREME-SCALE SCIENTIFIC INSIGHT Edited by E. Wes Bethel, Hank Childs, and Charles Hansen

INTRODUCTION TO COMPUTATIONAL MODELING USING C AND OPEN-SOURCE TOOLS

José M. Garrido

INTRODUCTION TO CONCURRENCY IN PROGRAMMING LANGUAGES Matthew J. Sottile, Timothy G. Mattson, and Craig E. Rasmussen

INTRODUCTION TO ELEMENTARY COMPUTATIONAL MODELING: ESSENTIAL CONCEPTS, PRINCIPLES, AND PROBLEM SOLVING José M. Garrido

#### PUBLISHED TITLES CONTINUED

INTRODUCTION TO HIGH PERFORMANCE COMPUTING FOR SCIENTISTS AND ENGINEERS

Georg Hager and Gerhard Wellein

INTRODUCTION TO REVERSIBLE COMPUTING

Kalyan S. Perumalla

INTRODUCTION TO SCHEDULING

Yves Robert and Frédéric Vivien

INTRODUCTION TO THE SIMULATION OF DYNAMICS USING SIMULINK  $^{\! \oplus \! }$  Michael A. Gray

PEER-TO-PEER COMPUTING: APPLICATIONS, ARCHITECTURE, PROTOCOLS, AND CHALLENGES

Yu-Kwong Ricky Kwok

PERFORMANCE TUNING OF SCIENTIFIC APPLICATIONS Edited by David Bailey, Robert Lucas, and Samuel Williams

PROCESS ALGEBRA FOR PARALLEL AND DISTRIBUTED PROCESSING Edited by Michael Alexander and William Gardner

SCIENTIFIC DATA MANAGEMENT: CHALLENGES, TECHNOLOGY, AND DEPLOYMENT Edited by Arie Shoshani and Doron Rotem

# THE GREEN COMPUTING BOOK

Tackling Energy Efficiency at Large Scale

## Edited by Wu-chun Feng

Virginia Polytechnic Institute and State University Blacksburg, USA

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business A CHAPMAN & HALL BOOK

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2014 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20130916

International Standard Book Number-13: 978-1-4398-1988-3 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

## **Table of Contents**

| Preface, ix |                                                                                |          |

|-------------|--------------------------------------------------------------------------------|----------|

| Contributor | rs, xvii                                                                       |          |

| Chapter 1 • | Low-Power, Massively Parallel, Energy-Efficient<br>Supercomputers              | <b>t</b> |

|             | IBM BLUE GENE TEAM*                                                            |          |

| Chapter 2 • | Compiler-Driven Energy Efficiency                                              | 43       |

|             | Mahmut Kandemir and Shekhar Srikantaiah                                        |          |

| Chapter 3 ■ | An Adaptive Run-Time System for Improving Energy Efficiency                    | 87       |

|             | Chung-Hsing Hsu, Wu-chun Feng, and Stephen W. Poole                            |          |

| Chapter 4 • | Energy-Efficient Multithreading through                                        | 110      |

|             | Run-Time Adaptation  Matthew Curtis-Maury and Dimitrious S. Nikolopoulus       | 115      |

| Chapter 5 ■ | Exploring Trade-Offs between Energy Savings and Reliability in Storage Systems | 149      |

|             | ALI R. BUTT, PURANJOY BHATTACHARJEE, GUANYING WANG,                            |          |

|             | and Chris Gniady                                                               |          |

| Chapter 6 • | Cross-Layer Power Management                                                   | 183      |

|             | Zhikui Wang and Parthasarathy Ranganathan                                      |          |

| Chapter 7 • | Energy-Efficient Virtualized Systems                                           | 231      |

|             | Ripal Nathuji and Karsten Schwan                                               |          |

| CHAPTER 8 • Demand Response for Computing Centers      | 267 |

|--------------------------------------------------------|-----|

| Jeffrey S. Chase                                       |     |

| CHAPTER 9 Implications of Recent Trends in Performance |     |

Costs, and Energy Use for Servers

JONATHAN G. KOOMEY, CHRISTIAN BELADY, MICHAEL PATTERSON, ANTHONY SANTOS, AND KLAUS-DIETER LANGE 297

**INDEX**, 321

### **Preface**

#### INTRODUCTION

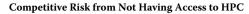

In 1957, the Soviet Union launched the first Earth-orbiting artificial satellite—Sputnik I—into space. This singular event precipitated the birth of the space age and, more specifically, the U.S.–U.S.S.R. space race. If we fast forward 45 years, the year is 2002, and Japan unveils the first supercomputer that obliterates U.S. domination in supercomputing,\* creating such a fervor that the event is dubbed Compute-nik and ignites an "arms race in supercomputing" in which the need for speed is paramount above all else and supercomputing (also referred to as high-performance computing or HPC) becomes increasingly mainstream, as illustrated in Figure 0.1 from the U.S. Council of Competitiveness, and as detailed in a report by the President's Information Technology Advisory Committee (PITAC).

However, this singular focus on speed as a performance metric arguably comes at the expense of other performance metrics, such as efficiency, reliability, and availability, to name a few. These "other" metrics are of particular interest to our *Supercomputing in Small Spaces (SSS)* project, which started in 2001, when being cool was "not cool." Why? With the supercomputing community's focus on speed, supercomputing nodes were not only becoming faster but also consuming and dissipating more power. By applying Arrhenius's equation to microelectronics or, more generally, computer hardware, every 10°C increase in temperature doubles the failure rate of a given system. This equation was supported by our own informal empirical data at the time, specifically a 128-node cluster that resided in a warehouse and failed approximately once per week during the winter months when the temperature inside the warehouse was 21–23°C and approximately twice per week during the summer months when the temperature was 30–32°C. As a consequence, we learned that by keeping the power draw lower, and

<sup>\*</sup>The Japanese supercomputer, called Earth Simulator, delivered a sustained performance that was approximately five times faster than the next-fastest supercomputer in the world.

$<sup>^\</sup>dagger Arrhenius$ 's equation notes that for many common chemical reactions at room temperature, the reaction rate doubles for every  $10^\circ C$  increase in temperature.

FIGURE 0.1 The importance of high-performance computing (HPC).

in turn system temperature lower, the efficiency, reliability, and availability of a supercomputer could be significantly improved. Furthermore, with 65% of information technology managers reporting that their websites were unavailable to customers over a 6-month period, and that the cost of the service outages ran as high as \$6,450,000/hour for a New York City stockbroker and \$1,200,000/hour for Amazon.com, businesses also require HPC (or, more broadly, large- or extreme-scale computing) that delivers near-100% availability with efficient and reliable resource usage in support of e-commerce, enterprise applications, and data centers.

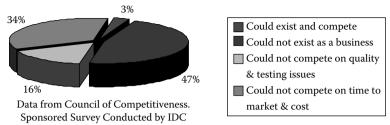

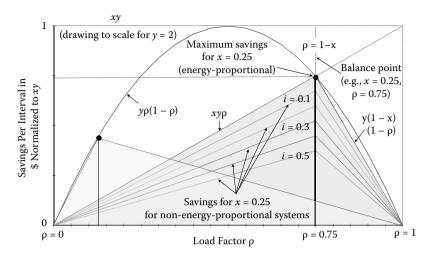

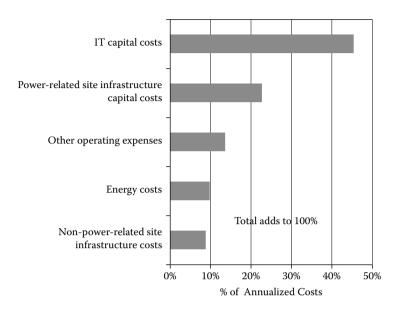

By the late 2000s, the data center community finally realized the need for energy-efficient HPC as the annual energy costs for a data center surpassed annual server purchase costs in 2008, as demonstrated in Figure 0.2. Around this same time frame, the supercomputing community also recognized the importance of both speed and power consumption in the context of tomorrow's exascale computing systems. For example, while past trends indicate that an exascale supercomputer (10<sup>18</sup> floating-point operations per second or 10<sup>18</sup> FLOPS) would arrive in 2018, such a system is projected to consume more than 100 megawatts (MW) of power, thus making power consumption the primary design constraint for achieving such exascale performance. Even the floating-point units (FPUs) alone are projected to consume 10 MW of power. Based on these projections, "performance at any cost" is no longer practical.

#### GREEN SUPERCOMPUTING: PAST, PRESENT, AND FUTURE

While the supercomputing community focused on performance (i.e., speed) in the early 2000s, as exemplified by the Top500 list (http://www.top500.org/) and the Gordon Bell Awards at the ACM/IEEE (Association for Computing Machinery/Institute of Electrical and Electronics Engineers)

FIGURE 0.2 Annual amortized costs in the data center.

Supercomputing Conference every year, I instead built *MetaBlade*, a 24-node cluster having a footprint of  $19 \times 25$  in. (or  $3.3 \text{ ft}^2$ ) and consuming a meager 300 watts (W) of power at idle, when booted diskless, in 2001. To put this into perspective, two large-size pizza boxes placed side by side have a footprint of  $16 \times 32$  in. (or  $3.5 \text{ ft}^2$ ), and the equivalent of three 100 W lightbulbs could power MetaBlade.

How was such a feat possible? Each processor (or central processing unit, CPU) in MetaBlade was a Transmeta TM5800 that ran our customized high-performance code-morphing software, which improved overall performance while maintaining a small thermal power envelope. Specifically, a Transmeta TM5600 CPU by itself dissipated only 6 W under load.

As a follow-up to MetaBlade and as the first major instantiation of the SSS project, MetaBlade was extended to create the *Green Destiny* supercomputer in April 2002 with the tenets of efficiency, reliability, and availability in mind. Green Destiny\* was a 240-node cluster with a slightly larger footprint than MetaBlade— $24 \times 30$  in. (or  $5.0 \, \text{ft}^2$ )—but approximately 14 times

<sup>\*</sup>The namesake for Green Destiny (GD) has a multiplicity of origins. First, the destiny of the GD was to be green. Second, GD was based on computer "blade" technology; GD was also the name of the sword blade in *Crouching Tiger, Hidden Dragon*. Third, the names of the groundbreaking supercomputers from the ASCI program at the U.S. Department of Energy were named after different colors; our project chose green.

taller than MetaBlade for a total volume of 32 ft<sup>3</sup>, which is approximately the size of a small telephone booth. The entire Green Destiny supercomputer consumed only 3.2 kW of power, roughly the equivalent in power to two hairdryers. Due in large part to its very low thermal power envelope, Green Destiny did not have any unscheduled downtime in its 2-year lifetime, despite residing in a dusty 85–90°F warehouse at over 7,000 ft above sea level. Because the CPUs in Green Destiny consumed so little power, the CPUs did not require active cooling, could be closely packed, and provided tremendous savings in terms of operational costs, space constraints, and cooling infrastructure. This audacious feat led to worldwide acclaim, including media coverage in *The New York Times*, CNN, and *PC World*, just to name a few.\* However, this feat did *not* lead to the worldwide embracement of the large-scale green computing movement, at least not at the time. It did, however, provide the impetus for significant seminal research in the area of large-scale green computing, as exemplified in this book.

This green book is organized into nine chapters and loosely ordered to start with low-level, hardware-based approaches and traversing up the software stack with increasingly higher-level, software-based approaches. Debuting in November 2004, the IBM Blue Gene approach to green supercomputing sets the stage in Chapter 1, "Low-Power, Massively Parallel, Energy-Efficient Supercomputers," authored by the IBM Blue Gene team. In this chapter, IBM architects focus on low-power, high-performance designs that illustrate how to improve the energy efficiency of a supercomputer by an order of magnitude without any system performance loss in parallelizable applications.

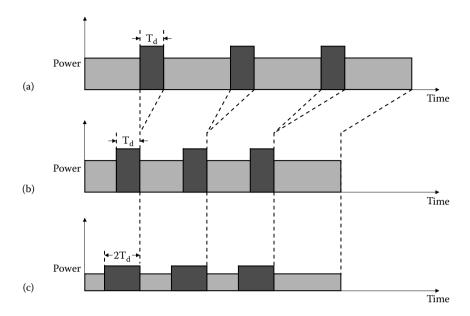

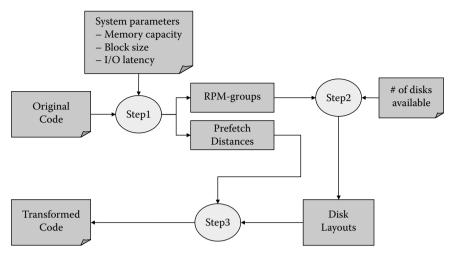

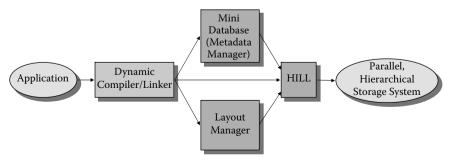

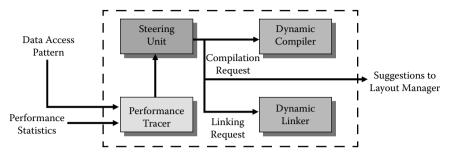

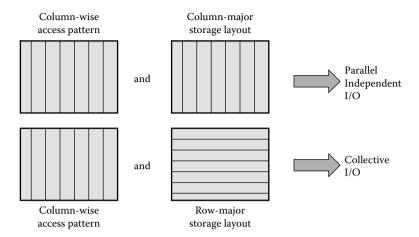

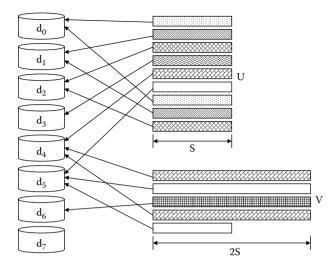

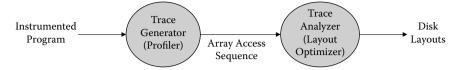

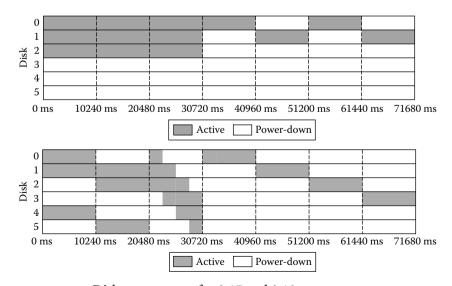

With the export of software-based mechanisms, such as dynamic voltage and frequency scaling (DVFS) and dynamic concurrency throttling (DCT), to control underlying computer hardware, the energy efficiency of a large-scale computing system can be enhanced further *if* these mechanisms are applied appropriately (i.e., at the right time and at the right setting). To that end, Chapter 2, "Compiler-Driven Energy Efficiency," by Kandemir and Srikantaiah seeks to reshape a program either explicitly, by inserting instructions to turn off resources that are not being used, or implicitly, by increasing the idle periods between two usages of the resource. In particular, the authors demonstrate this via compiler-directed energy optimizations in both the I/O (input/output) subsystem and the network on a chip (NoC), which can consume significant power due to on-chip communication.

<sup>\*</sup>Green Destiny and an identical replica of it now reside in the Computer History Museum in Mountain View, California, and in the Bradbury Science Museum in Los Alamos, New Mexico, respectively.

As a complement to the compiler-driven approach mentioned, Hsu, Feng, and Poole present their dynamic run-time system that *automatically* schedules the DVFS mechanism at the right voltage and frequency and at the right time to maintain performance while reducing both power and energy consumption. Serendipitously, the work in Chapter 3, "An Adaptive Run-Time System for Improving Energy Efficiency," was in response to criticism of Green Destiny and, in turn, as an outgrowth of the SSS project. Specifically, many criticized Green Destiny for sacrificing too much performance to reduce power consumption, while others complained that Green Destiny used too many pseudoproprietary parts. By leveraging DVFS on commodity processors from AMD, the adaptive run-time system presented in Chapter 3 addresses these criticisms in one fell swoop and has since been adapted to other commodity processors.

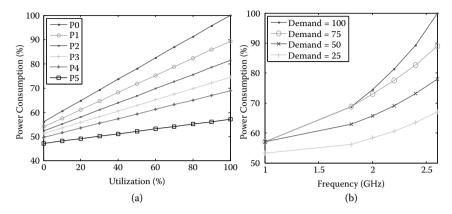

Similarly, Chapter 4, "Energy-Efficient Multithreading through Run-Time Adaptation," by Curtis-Maury and Nikolopoulus presents a general framework that predicts the performance impact of dynamically adjusting different power-performance settings and derives predictors to efficiently identify optimal settings at run time. The framework simultaneously leverages both DVFS and DCT across multiple multicore processors. In addition, this chapter provides a survey of methods for power-performance adaptation in run-time systems.

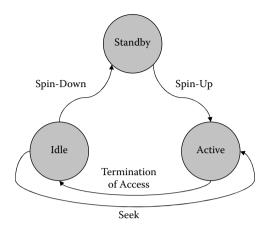

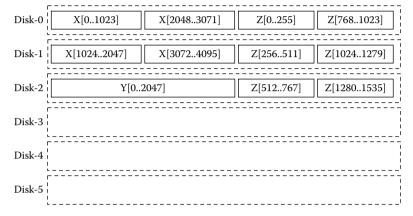

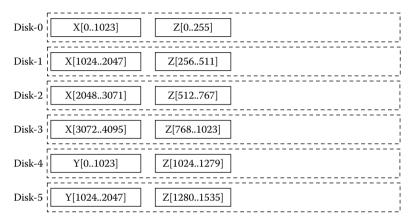

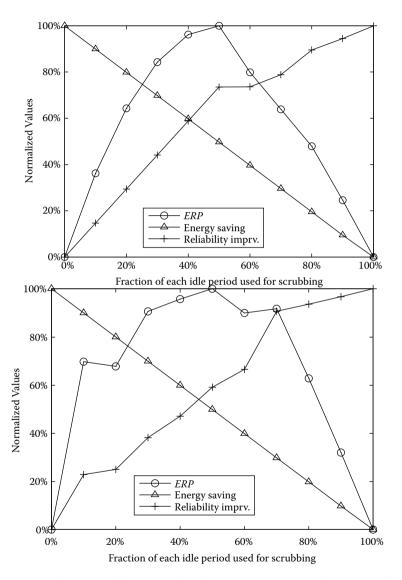

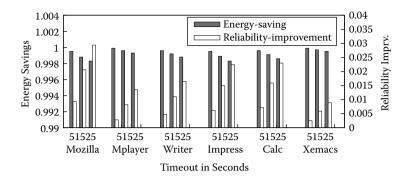

Chapter 5, "Exploring Trade-Offs between Energy Savings and Reliability in Storage Systems," by Butt, Bhattacharjee, Wang, and Gniady not only explores the interactions between energy management and reliability but also studies storage system organization that maximizes energy efficiency and reliability. To support these items, the authors propose a new metric for simultaneously evaluating energy and reliability called the energy-reliability product (ERP) and the basic mechanisms for idle time allocation between energy management and reliability mechanisms to achieve a balance between energy consumption and reliability.

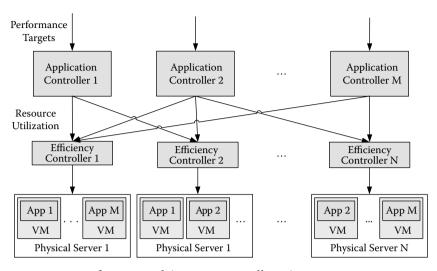

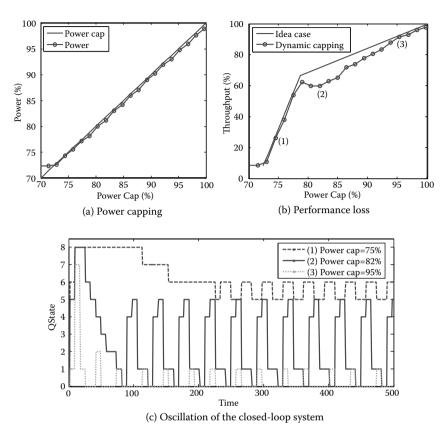

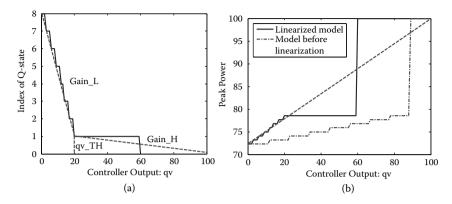

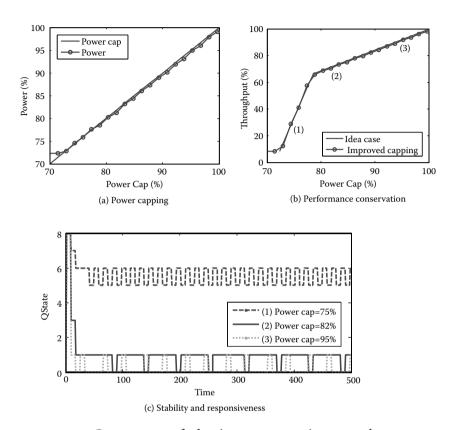

From a more holistic perspective, Chapter 6, "Cross-Layer Power Management," by Wang and Ranganathan addresses the need for coordinated power control across different layers: hardware, firmware, operating system (OS), and application level. The authors identify a key challenge that arises when multiple controllers at different layers interfere with each other due to the lack of adequate coordination between the controllers and then present the benefits of cross-layer power management solutions.

In Chapter 7, "Energy-Efficient Virtualized Systems," Nathuji and Schwan discuss the nexus of two problem domains, energy management

and virtualization, which are proving to be critical for cloud computing environments and the data centers that house them. Specifically, the authors articulate how current virtualization systems lack the capability to perform active power management while still supporting quality-of-service requirements. They then describe ways for extending existing virtualization architectures to better support energy efficiency.

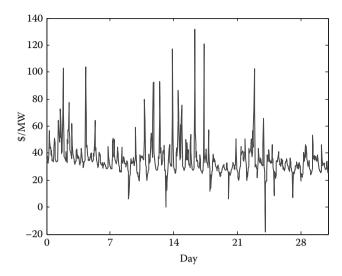

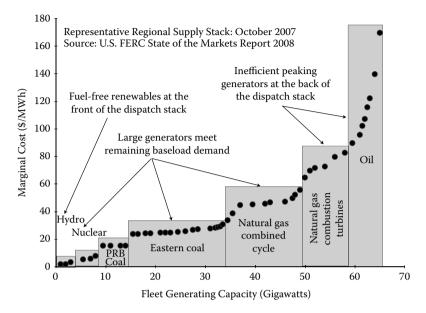

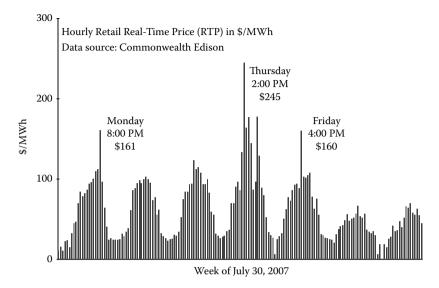

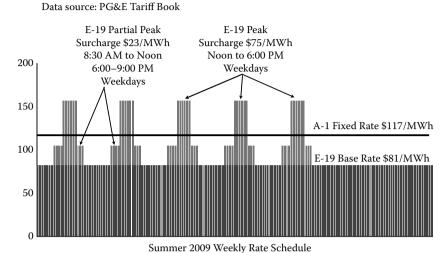

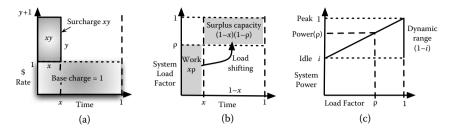

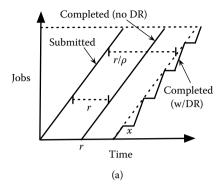

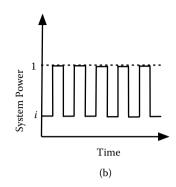

As conveyed in its title, "Demand Response for Computing Centers," Chapter 8 by Chase studies the demand response (DR) in computing centers, where DR refers to policies that influence the timing or location of power demand when responding to signals from the electrical supplier about energy production cost or availability. This, in turn, is intended to improve the reliability and efficiency of electrical power grids and the myriad associated "smart grid" initiatives.

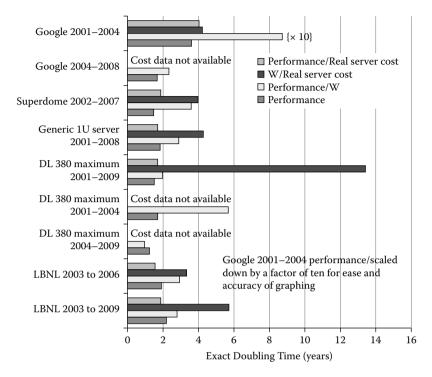

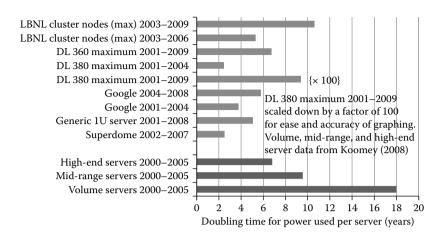

Finally, Chapter 9, "Implications of Recent Trends in Performance, Costs, and Energy Use for Servers," by Koomey, Belady, Patterson, Santos, and Lange assesses trends in servers and their impact on data center costs. Specifically, the authors summarize trends in server costs, energy use, and performance and then describe the implications of these trends in the context of the economics of high-density computing facilities.

In addition to the contributing authors of this book, there are many people to thank for their role in its realization. First and foremost, I thank Horst Simon for providing me with the opportunity to create this book as a consequence of my early (and controversial) research in green supercomputing with Green Destiny, its evolution into a software-based approach called *beta* (see Chapter 3) and commercially known as EnergyFit, and the subsequent initiation of the Green500 (http://www.green500.org/). As the Chapman & Hall/CRC Computational Science Series editor, Horst provided guidance in shaping the book and served as a source of inspiration with his pursuit of energy efficiency for large-scale computing systems, as exemplified by his tireless efforts toward realizing the University of California's Computational Research and Theory (CRT) Facility.

Many thanks to Randi Cohen, computer science acquisitions editor for Chapman & Hall/CRC Press, who was critical in the development and production of this book. Without her assistance, support, cajoling, and patience, this book would not have been possible.

Finally, I thank my wife, Annette Feng, and children, Akaela and Kai, for their understanding and patience while I juggled the demands of work, the preparation of this book, and family time.

I hope that this green book inspires you the way that it has inspired the authors and me to write about it and to raise the awareness of *greenness* as a first-order design constraint that is on par with performance. As a tongue-in-cheek comment, we hope that this book will encourage data centers and supercomputing centers to simulate climate change rather than "create it."

## Contributors

#### **Christian Belady**

Microsoft

Seattle, Washington

#### Puranjoy Bhattacharjee

Amazon Seattle, Washington

#### Ali R. Butt

Virginia Tech Blacksburg, Virginia

#### Jeffrey S. Chase

Duke University

Durham, North Carolina

#### George Chiu

IBM T.J. Watson Research Center Yorktown Heights, New York

#### **Matthew Curtis-Maury**

NetApp Raleigh, North Carolina

#### Wu-chun Feng

Virginia Tech Blacksburg, Virginia

#### Chris Gniady

University of Arizona Tucson, Arizon

#### **Chung-Hsing Hsu**

Oak Ridge National Laboratory Oak Ridge, Tennessee

#### IBM Blue Gene Team®

IBM T. J. Watson Research Center Yorktown Heights, New York

#### Mahmut Kandemir

Pennsylvania State University State College, Pennsylvania

#### Jonathan G. Koomey

Stanford University Palo Alto, California

#### Klaus-Dieter Lange

Hewlett-Packard Houston, Texas

#### Ripal Nathuji

NeoTek Labs Austin, Texas

#### **Dimitris Nikolopoulos**

Forth Institute of Computer Science Crete, Greece

#### Michael Patterson

Stanford University Palo Alto, California

#### xviii ■ Contributors

#### Stephen W. Poole

Oak Ridge National Laboratory Oak Ridge, Tennessee

#### Parthasarathy Ranganathan

Google

Mountain View, California

#### **Anthony Santos**

Stanford University Palo Alto, California

#### Karsten Schwan

Georgia Tech Atlanta, Georgia

#### Shekhar Srikantaiah

Penn State University College Station, Pennsylvania

#### **Guanying Wang**

Virginia Tech Blacksburg, Virginia

#### Zhikui Wang

HP Labs Palo Alto, California

## Low-Power, Massively Parallel, **Energy-Efficient** Supercomputers

IBM Blue Gene Team\*

#### **CONTENTS**

| 1.1 | Introduction                             | 2 |

|-----|------------------------------------------|---|

| 1.2 | Voltago Scaling in Hardware Technologies | 1 |

Voltage Scaling in Hardware Technologies

\*IBM: P.V. Allen, C.J. Archer, R.G. Archambault, S. Asaad, J.E. Attinella, J. Balster, J.R. Behun, R.E. Bellofatto, J.R. Bentlage, H.R. Bickford, S.K. Birkholz, M. Blocksome, M.A. Blumrich, A. Boulter, T.C. Brennan, J.J. Brewer, B. Brezzo, A.A. Bright, J.R. Brunheroto, T.A. Budnik, L. Chang, J.D. Chauvin, D. Chen, C.-Y. Cher, G. L.-T. Chiu, T.M. Cipolla, P.W. Coteus, A. Curioni, P. Curtis, K. Davis, M. Deindl, R.H. Dennard, B. Deskin, W. Donegan, J. Doi, M.B. Dombrowa, S.M. Douskey, G. Dozsa, A.E. Eichenberger, D. Eisenmenger, N.A. Eisley, M.R. Ellavsky, S.D. Ellis, K.C. Evans, S.T. Evans, G.A. Fax, A. Ferencz, S. Fetterolf, J.T. Ficke, G. Fiorenza, B.G. Fitch, R.A. Fitch, B.M. Fleischer, W.T. Flynn, T.W. Fox, D.J. Frank, R.L. Franke, S. Frei, M. Fritsch, D.S. Gallo, A Gara, R. Germain, P.R. Germann, M.E. Giampapa, F.P. Giordano, M.P. Good, T.M. Gooding, M.K. Gschwind, J.A. Gunnels, W.H. Haensch, S.A. Hall, M.J. Hamilton, R.A. Haring, J.S. Harveland, P. Heidelberger, T.D. Helvey, D. Hoenicke, R. Hoover, B.J. Hruby, T.A. Inglett, D.J. Iverson, H. Jacobson, G. Janssen, M.J. Jeanson, M.C. Johnson, S.P. Jones, J.N. Judd, K.T. Kaliszewski, R. Kammerer, M. Kapur, F. Kasemkhani, M. Kaufmann, K.H. Kim, B.L. Knudson, S. Koch, M. Kochte, B. Koehler, G.V. Kopcsay, J. Kriegel, E. Kronstadt, S. Kumar, D.E. Lackey, A.P. Lanzetta, C. Lappi, J.A. Lawrence, D.A. Lawson, G.S. Leckband, S. Lee, R.F. Lembach, T.A. Liebsch, D. Littrell, K.C. Lyndgaard, R.W. Lytle, S.H. Mack, C.D. Malone, A. Mamidala, I. Mani, J.A. Marcella, C.M. Marroquin, C.H. Mathiowetz, M.D. Maurice, M.K. McManus, M.G. Megerian, M.P. Mendell, V. Metayer, S.J. Miller, T. Moe, R.K. Montoye, J.H. Moreno, M.B. Mundy, R.G. Musselman, T.E. Musta, I.I. Nair, B.J. Nathanson, Y. Negishi, E. Nelson, M.T. Nelson, C. Nilsen, C.F. Obert, K. O'Brien, A.S. Ohmacht, M. Ohmacht, D. Olson, J.L. Van Oosten, J.P. Orbeck, M.R. Ouellette, M.J. Palmer, J.J. Parker, D.P. Paulsen, K.P. Pfarr, R.A. Rand, M. Rangarajan, J. Ratterman, D.D. Reed, M.T. Repede, D.M. Rickert, T. Roewer, B.S. Rosenburg, M.G. Rosenfield, J.J. Ruedinger, K.D. Ryu, Y. Sabharwal, V. Salapura, D.L. Satterfield, J. Sawada, M. Schaal, P.E. Schardt, M.J. Scheckel, B. Schenck, H.J. Schick, D. Schmunkamp, R.L. Schoen, A.A. Schram, B.A. Schuelke, S. Schwartz, F.W. Sell, G.W. Sellers, R.M. Senger, J.C. Sexton, V.V. Shah, R.H. Sharrar, R. Shearer, J.E. Sheets, E. Shmueli, B. Smith, K.M. Solie, S.A. Strissel, B.D. Steinmacher-Burow, W.M. Stockdell, C. Stunkel, K. Sugavanam, Y. Sugawara, N. Suginaka, T. Takken, A.T. Tauferner, J.L. Thomas, S. Tian, J.A. Tierno, M.R. Tubbs, I. Vo, S. Wahl, C.D. Wait, R.E. Walkup, A.T. Watson, B.B. Winter, B. Wirtz, R.W. Wisniewski, G. Zhang, P.P. Zhao, M.M. Ziegler, C.G. Zoellin, L. Zumbrunnen. Columbia University: N.H. Christ. Columbia University and Riken BNL: C. Kim. Independent: B. Ji. University of Edinburgh: P.A. Boyle. University of Minnesota: S.J. Koester.

|      | 1.2.1       | Low-Voltage Scaling of Active Devi | ices 4 |

|------|-------------|------------------------------------|--------|

|      | 1.2.2       | On-Chip Digital Noise              | 6      |

|      | 1.2.3       | Power Delivery                     | 8      |

|      | 1.2.4       | Off-Chip Connections               | 12     |

|      | 1.2.5       | Cooling                            | 13     |

| 1.3  | Blue (      | Blue Gene Hardware                 |        |

|      | 1.3.1       | Voltage Scaling                    | 16     |

|      | 1.3.2       | Low-Power Floating-Point Units     | 20     |

|      | 1.3.3       | Power Delivery                     | 20     |

|      | 1.3.4       | Off-Chip Connections               | 21     |

|      | 1.3.5       | Cooling                            | 22     |

| 1.4  | Systen      | n Software                         | 24     |

|      | 1.4.1       | Overview                           | 24     |

|      | 1.4.2       | System Monitoring                  | 26     |

|      | 1.4.3       | Job History                        | 27     |

|      | 1.4.4       | Operational Phases                 | 28     |

|      |             | 1.4.4.1 Deallocated                | 29     |

|      |             | 1.4.4.2 Booting                    | 30     |

|      |             | 1.4.4.3 Allocated                  | 30     |

|      |             | 1.4.4.4 Running                    | 31     |

|      | 1.4.5       | Low-Power Implications on Softwa   | are 32 |

| 1.5  | Applio      | cations                            | 33     |

| 1.6  | Conclusions |                                    |        |

| Ackr | nowledgr    | nents                              | 37     |

| Refe | rences      |                                    | 38     |

#### 1.1 INTRODUCTION

Historically, power considerations have forced the electronics industry to evolve from vacuum tubes, to bipolar device technology, then to NMOS (n-type metal-oxide semiconductor), and finally to CMOS (complementary metal-oxide semiconductor) technology. For the past four decades, steady lithographic advancements have enabled higher integration, leading to exponentially decreasing cost per function, a trend commonly referred to as Moore's law [1]. For the larger part of this period, the semiconductor industry could follow the scaling guidelines developed by Dennard and coworkers [2] to design ever-smaller devices that could operate at ever-higher speeds while keeping power density constant. In recent years, however, fundamental physical limitations have caused CMOS technology to deviate from this

ideal device scaling. While trying to maintain speed and density improvements, the industry had to give up on keeping power density constant. Consequently, power dissipation has become a growing concern. Whereas in the past from one device generation to the next we could shrink lithography by a factor  $\sqrt{2}$  and expect two times more transistors in the same area while maintaining the same power density, we now find that power nearly doubles for those two times more transistors. Since power is already a constraint across all platforms, from handheld consumer devices to workstations, mainframes, and high-performance computing (HPC) systems [3–7], this is unwelcome news.

CMOS technologies in the 45-nm generation and beyond will require novel solutions to meet the challenge of power efficiency. However, the widespread adoption of parallelism, such as multicore and many-core architectures, in today's computing systems [4–7] creates new opportunities for power/performance optimization. To capitalize on these opportunities, the trade-offs in technology, circuits, and systems design will have to be evaluated from a systems perspective.

Because computing applications span a wide range of power and performance targets, as well as activity factors, the term low power can be interpreted in many different ways. This chapter does not focus on lowactivity-factor applications, ranging from sensor networks to portable applications, which only require intermittent compute capacity. Power dissipation for such low-activity-factor applications is dominated by standby power. Known techniques that can effectively mitigate standby power in such applications include clock gating, power gating [8], and the adjustment of transistor threshold voltages and gate dielectric thicknesses. Instead, this chapter addresses the more fundamental issue of reducing dissipation in the active mode, which is particularly relevant to applications with high-performance requirements and a high activity factor. We discuss low-power technologies as well as architectural innovations that reduce power consumption in such a context.

In the following analysis, performance and power are considered to be system-level metrics to be optimized. The system is assumed to consist of core logic and its associated cache memory, off-chip main memory, and a power delivery system. While such elements conceptualize the primary components of a parallel supercomputer, many other computer applications are similarly organized. It is important to note that the total power in such systems includes significant contributions from many sources—not simply the processor itself [9].

Section 1.2 analyzes voltage scaling, which enhances power efficiency in the overall system. Section 1.3 presents a practical case study of the IBM Blue Gene® systems. The low-power techniques described here demand an increase in parallelism to compensate for a reduction in operating frequency. Section 1.4 presents the Blue Gene system software and Section 1.5 the Blue Gene applications. In Section 1.5, we demonstrate that the majority of applications for which power efficiency is critical can be effectively parallelized to increase system-level performance in the range of interest. Thus, we can trade off power efficiency, frequency, and parallelism in a systems design.

#### 1.2 VOLTAGE SCALING IN HARDWARE TECHNOLOGIES

#### 1.2.1 Low-Voltage Scaling of Active Devices

For many years, CMOS voltage reduction occurred in conjunction with the reduction of technology dimensions. During this time, the scaling of MOS field-effect transistors (MOSFETs) largely followed the theory outlined in Table 1.1, which was originally proposed in Reference 2. By applying a suitable scale factor to each technology parameter, constant electric fields can be maintained throughout the device as it shrinks in size. Such a strategy protects against short-channel effects and maintains device reliability; more important, it results in reduced circuit delay without increasing power density. While many important advances in transistor technology

TABLE 1.1 Scaling Theory to Maintain Constant Electric Fields in a MOSFET Device

| <b>Device or Circuit Parameter</b>    | Scaling Factor |

|---------------------------------------|----------------|

| Device dimension $t_{ox}$ , $L$ , $W$ | $1/\kappa$     |

| Doping concentration $N_a$            | κ              |

| Voltage V                             | $1/\kappa$     |

| Current I                             | $1/\kappa$     |

| Capacitance $\varepsilon A/t$         | $1/\kappa$     |

| Delay time/circuit VC/I               | $1/\kappa$     |

| Power dissipation/circuit VI          | $1/\kappa^2$   |

| Power density VI/A                    | 1              |

|                                       |                |

Source: Copyright from L. Chang, D. J. Frank, R. K. Montoye, S. J. Koester, B. L. Ji, P. W. Coteus, R. H. Dennard, and W. Haensch, *IEEE Proc.*, 98(2), 215–236, February 2010. κ is a dimensionless scale factor.

have been made through the years, the basic structure has not changed significantly, and these scaling guidelines, first proposed over 35 years ago, are still relevant.

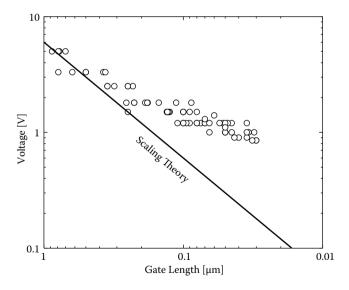

As CMOS technologies entered the submicron regime, several fundamental issues led to the modification of these scaling rules [10]. In particular, due to nonscalability of the threshold voltage and underlying limits on the subthreshold slope, supply voltage scaling slowed and in recent years has essentially come to a halt. Difficulties in scaling the gate dielectric thickness have also contributed to this trend, as a minimum gate dielectric thickness will have to be maintained to limit leakage power. Consequently, a minimum gate voltage will have to be applied to maintain the electric field and device performance. In addition, as manufacturing variability has a mounting influence on device characteristics, it has been prudent in some cases to raise voltages as a precaution to preserve operating margins. As a consequence, as shown in Figure 1.1, the supply voltage in modern technologies is significantly higher than originally suggested by a scaling theory [11].

FIGURE 1.1 Scaling trend for power supply voltages in modern CMOS technologies. Due to leakage and variability constraints, voltage levels have deviated significantly from a constant field scaling theory [3]. (Copyright from L. Chang, D. J. Frank, R. K. Montoye, S. J. Koester, B. L. Ji, P. W. Coteus, R. H. Dennard, and W. Haensch, IEEE Proc., 98(2), 215-236, February 2010.)

To first order, power dissipation in the active mode can be expressed as

$$P_{active} = C_{eff} V^2 f + I_{leak} V (1.1)$$

where  $C_{eff}$  is the total effective load capacitance of a chip (a more precise definition is given in Section 1.3), V is the operating voltage, f is the operating frequency, and  $I_{leak}$  is the total aggregate leakage current of active devices when not being switched. The first term is the dynamic power dissipation due to switching, while the second term is the power consumed by leakage. Since  $C_{eff}$  is weakly dependent on voltage, the combined effective voltage dependence of  $C_{eff}V^2$  has an exponent closer to 2.5 [12]. Empirically, it has been observed that the maximum operating frequency for a wide variety of circuits is a linear function of voltage in the regime of interest. An expression for frequency can thus be written as

$$f = \alpha(V - V_0) \tag{1.2}$$

where  $V_0$  is the voltage at which the frequency approaches zero ( $\sim$ 0.25 V for modern technologies), and  $\alpha$  is a constant that depends on the circuit. This same relation also applies to circuits that are optimized at each voltage, but with somewhat higher  $V_0$  ( $\sim$ 0.3–0.4 V) since low-voltage technologies generally optimize to higher threshold voltages. Putting these equations together yields

$$P_{active} = \alpha C_{eff} V^2 (V - V_0) + I_{leak} V \tag{1.3}$$

While  $I_{leak}$  has a strong dependence on voltage, design optimization tends to maintain a consistent ratio between switching and leakage dissipation such that the overall voltage dependence of  $P_{active}$  is roughly cubic. Operating voltage is thus clearly the most effective parameter through which power dissipation can be improved. A reduction in voltage, however, limits operating frequencies and inevitably degrades the performance of a given circuit. In accordance with current trends [13], system-level performance can be regained with additional parallel circuit blocks, which linearly adds to power dissipation. Since the superlinear improvements in power due to voltage scaling outweigh the linear increase in power due to parallelism, the end system can see substantial gains in power efficiency.

#### 1.2.2 On-Chip Digital Noise

While active transistors discussed in the previous sections can help to maintain logic performance and memory circuit functionality at low supply

voltages, it must also be ensured that signals propagated on properly scaled passive interconnects [13, 14] at these low voltages are resilient to those noise sources relevant to digital circuits. A common initial reaction to voltage scaling is that susceptibility to noise is increased—that at a constant noise level, a reduction in operating voltage could compromise margins. It is important to remember, however, that the noise sources relevant to digital circuit operation will scale with voltage, and that the end impact on circuit functionality may, in fact, improve. It will thus be argued in this section that such on-chip digital noise should not be of concern if voltages continue to be scaled.

Generally, digital CMOS circuits are quite tolerant of noise, but operating margins for some circuits can be small. In particular, dynamic logic can suffer from charge leakage problems, while latches may see degraded setup and hold times. Such voltage noise can be caused by resistive drops, capacitive charge coupling, and inductive transients.

With appropriate consideration of scaling factors, each of these noise sources decreases in importance as voltages are lowered. It should be noted that this discussion neglects mechanisms such as thermal, shot, and 1/f noise. While important for analog circuits, such noise is not generally a concern for digital circuits.

Resistive voltage drops as a fraction of the power supply voltage are related to the current drive I of a given device and the characteristic resistance R of the wiring path in question:

$$\frac{\Delta V_R}{V_{DD}} = \frac{IR}{V_{DD}} \propto \frac{(V_{DD} - V_T)^{1.5}}{V_{DD}}$$

(1.4)

Since R is not a function of voltage, this expression depends only on I, which, for the purposes of this discussion, can be expressed as a power law function of the gate overdrive voltage [15], where the exponent is assumed here to be about 1.5 for modern CMOS technologies. Since *I* is a superlinear function of  $V_{DD}$ , it scales faster than  $V_{DD}$ , and the expression can be seen to decrease with voltage scaling for relevant values of  $V_{DD}$  and  $V_T$ . Thus, resistive voltage drops become less of a concern with voltage scaling.

Voltage noise due to capacitive coupling occurs when an aggressor of parasitic capacitance  $C_{agg}$  switches by a potential difference of  $V_{DD}$  and acts on a victim load capacitance  $C_{vic}$ :

$$\frac{\Delta V_C}{V_{DD}} = \frac{\frac{C_{agg}V_{DD}}{C_{vic} + C_{agg}}}{V_{DD}} = \frac{C_{agg}}{C_{vic} + C_{agg}}$$

(1.5)

The magnitude of this coupling noise as a fraction of  $V_{DD}$  is thus determined by the capacitive divider between the victim and aggressor and is not a function of voltage. Thus, voltage noise due to capacitive coupling scales with  $V_{DD}$  and does not worsen.

Inductive voltage noise arising from current transients can be calculated as

$$\frac{\Delta V_L}{V_{DD}} = \frac{L\frac{\partial I}{\partial t}}{V_{DD}} \propto \frac{LI}{V_{DD}\tau} \propto \frac{(V_{DD} - V_T)^{1.5}(V_{DD} - V_0)}{V_{DD}}$$

(1.6)

where  $\tau$  is the characteristic time of such current spikes, which is related to the operating frequency of the circuit in question, which, from Equation 1.2, is linearly dependent on  $V_{DD}$ . This overall expression is a superlinear function of  $V_{DD}$ , which means that inductive noise scales faster than  $V_{DD}$  and thus only improves with voltage scaling.

#### 1.2.3 Power Delivery

Assuming that low-voltage logic and memory solutions are available, and digital noise is contained, the next requirement is to ensure that this low-voltage supply is efficiently and accurately delivered to the chip. Without appropriate consideration of the power delivery system, excessive voltage margins may be needed, which can counteract the gains achieved by successful on-chip voltage scaling. Already today, at about 1-V supplies, the power loss and noise in the path from the external power source to the circuits on a chip can be significant. When voltage is reduced to improve power efficiency at constant performance, total power is lowered, which improves power supply efficiency and stability. However, in scenarios that increase parallelism beyond this point to improve system-level performance, the power supply efficiency and stability may become severely degraded, and advancements in chip packaging or point-of-load power conversion will be required.

In a traditional power delivery system, an off-chip DC-DC (direct-current-to-direct-current) converter normally regulates the supply voltage. The power is then delivered to, and distributed throughout, the chip via a power grid. Nonnegligible power loss occurs in the power delivery network due to Joule heating, which degrades power efficiency. For a system to deliver a power P at a voltage V and total current Ithrough a power delivery line of effective resistance R, the power loss is given by

$$\frac{P_{loss}}{P} = \frac{I^2 R}{P} = \frac{(P/V)^2 R}{P} = \frac{PR}{V^2}$$

(1.7)

While a reduction in voltage could increase power loss, the corresponding drop in power dissipation levels more than compensates since the dependence of power on voltage in Equation 1.3 is more than cubic. Assuming that parallelism is achieved at the system level and not by growing chip size, it can be assumed that the resistance remains constant. Thus, power delivery efficiency for a fixed design may not degrade but might in fact be improved with voltage scaling.

Supply variation due to sudden load changes can result in a voltage drop, which can be calculated as

$$\frac{\Delta V_L}{V} = \frac{L\frac{dI}{dt}}{V} \propto \frac{\Omega L P}{V^2} \tag{1.8}$$

where L is the inductance of the power distribution network, and  $\Omega$  is the characteristic frequency over which current loads change (which might be related to the distribution network rather than the voltage-dependent chip operating frequency). As with power loss [15], supply variation scales well with voltage, primarily due to reduced power dissipation levels. The additional dependence on frequency may further suppress supply noise at low voltages—rendering instability a less-critical issue than power delivery efficiency. However, it should be remembered that circuits operating at low voltage may be more sensitive to supply variations. It should also be noted that this issue can also be improved by the addition of more decoupling capacitance.

In the optimizations of Section 1.2.1, voltage scaling will improve power efficiency at constant system performance (i.e., constant  $C_{eff}x$  f), which, as stated previously, results in power delivery efficiency and manageable supply variation issues. However, the savings in power due to voltage scaling could instead be used to maximize the number of parallel units for a given power budget, which will improve system performance at constant total power. The number of parallel units could be increased dramatically constrained only by cost and physical chip size limits. In this constant power scenario, Equations 1.7 and 1.8 indicate that power delivery efficiency and supply variations could worsen significantly with voltage scaling. Thus, new methods of power delivery may be needed.

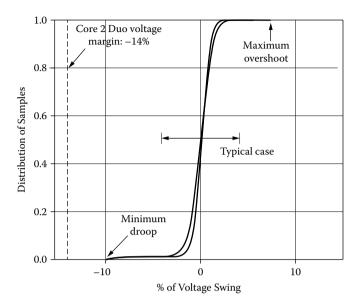

Vijay Janapa Reddi and colleagues have studied the voltage variation of the Intel Duo processor in detail [16]. In Figure 1.2 from their paper [16], the voltage of an Intel Core<sup>TM</sup> 2 Duo processor is measured for a variety of workloads. The voltage droops by as much as 9.6% from the nominal, or set point, voltage, which was set 14% above the voltage required for

FIGURE 1.2 Voltage measured on the Intel Core 2 Duo processor for a series of workloads. In the worst case, voltage sag was 9.6%, for which the nominal processor voltage was set 14% high. (From V. J. Reddi, S. Kanev, W. Kim, S. Campanoni, M. D. Smith, G.-Y. Wei, and D. Brooks, IEEE Micro, pp. 20–26, January/Febuary 2011.)

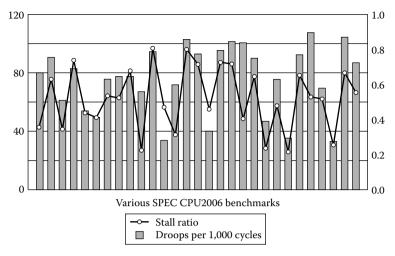

error-free operation. The authors found a very high correlation between voltage variation and processor stalls, as seen in Figure 1.3. This is easily understood as the voltage undershoot L dI/dt that occurs as the processor moves from the low-power to the high-power state following a stall. Although the authors found some opportunity for software-based predictive algorithms, which may allow a suitable engineered system to operate with voltage closer to the edge of failure, this dramatic voltage variation is predicted by the authors only to worsen in future multicore processor designs.

We expect continued improvements in the efficiency of both alternating current (AC)-to-DC converters and external DC-DC converters. However, unless chip-packaging techniques can be dramatically changed to reduce both resistance and inductance, a new strategy is required to efficiently deliver stable power at low voltage. In modern computer systems, an explosion of different voltages further aggravates the problem. As core voltage falls, other voltages in the form of references, SRAM (static random-access memory) wordline boost voltages, input/output (I/O) driver voltages, receiver

FIGURE 1.3 Voltage droop versus a stall ratio, explained by the authors as a combination of various counters in the processor indication program stall. The correlation between the change from low to high power as indicated by the extent of the stall, and the resultant L di/dt voltage droop, is apparent. (From V. J. Reddi, S. Kanev, W. Kim, S. Campanoni, M. D. Smith, G.-Y. Wei, and D. Brooks, *IEEE Micro*, pp. 20–26, January/Febuary 2011.)

threshold voltages, and the like are proliferating. As a result, a modern computer system can require many different voltages, most of which have modest current demands. This points to an opportunity for on-chip DC-DC voltage conversion. The mix of on-chip and off-chip DC-DC conversion will depend on the area and efficiency of the two solutions. Resistive series regulators are fundamentally limited to low (~50%) conversion efficiencies due to the inherent resistive divider network and thus are unsuitable for on-chip voltage conversion. Buck converter techniques, utilizing on-chip inductors, are more efficient, but practical implementations have been limited to about 75% due to difficulties in achieving on-chip inductors with high-quality factors. Instead, switched-capacitor circuits may be an effective solution for on-chip voltage conversion. Such circuits traditionally suffer from limitations in efficiency [17], but recent advancements in process technology can potentially enable on-chip conversion efficiencies of more than 90%. The improvement is primarily due to the availability of trench capacitor structures in high-performance CMOS processes. Trenches used for embedded DRAM (dynamic RAM) [18] yield capacitors of very high density with minimal stray parasitics. In addition, with technology scaling,

the MOSFETs used as switching devices become quite efficient at the 45-nm node and beyond.

#### 1.2.4 Off-Chip Connections

Combined, solutions to the aforementioned issues can enable low-voltage operation of a chip to improve power efficiency. However, any chip must always communicate with the rest of the system, and this can dissipate significant power. In particular, in many applications, much of the power associated with the memory subsystem can be attributed to such interconnections. Especially for future exascale applications, which will demand extreme memory bandwidth, it is imperative to find solutions that reduce power in off-chip connections.

Off-chip connections that are relatively short, or otherwise operating in a high-quality channel, can be thought of as lossless. Depending on available packaging strategies, such connections can comprise a significant portion of overall I/O power—especially with rising needs in cache bandwidth close to the processor. Without attenuation concerns, the driver and receiver circuits are relatively simple, and the power needed to drive the connection itself can dominate. For these short connections, the active power can be expressed as

$$P_{I/O} = C_{I/O} V^2 f_{eff} (1.9)$$

where  $C_{I/O}$  is the interconnect capacitance, V is the operating voltage, and  $f_{eff}$  is the effective frequency—considering application-dependent activity factors—at which the connection is operated. Clearly, scaling of the output voltage range in these interconnect driver circuits is an effective method by which power could be reduced. The introduction of a locally generated and regulated low-voltage supply can enable a power-efficient, low-voltage driver. On the receiving end, a single-ended sense amplifier, such as enabled by a gated diode device [19], can provide efficient, low-voltage signal recovery. Together, these components can minimize power in low-loss connections. As long as the voltages of all connections are scaled together, signal cross talk can be minimized. For short interconnections that follow Equation 1.9, it may also be possible to reduce interconnect capacitance and the effective frequency of operation. In particular, advanced packaging techniques such as three-dimensional integration via wafer bonding [20] or silicon carriers [21] bring chips closer together, which can eliminate transmission line effects, reduce capacitance, and decrease power as compared with traditional I/O pins and board-level wiring. Ultimately, continued density scaling and single-chip integration will shorten many off-chip connections.

For longer-reach interconnections, which suffer from losses due to highfrequency attenuation, it may be possible to utilize low signal swing to reduce power [22]. But, ultimately, channel quality limits the practicality of such techniques, as the transceiver circuits will tend to dominate total power. Recent work on low-power serial links has focused on equalization techniques [23-25], which may benefit somewhat from the general CMOS voltage-scaling strategies described in this chapter. However, voltage scaling in analog circuits may be limited, and parallelism is likely not a viable solution in this case. Thus, ultimately, optical interconnects [26] will likely be required to achieve significant power reduction in long-range links.

It should be noted that the power associated with off-chip connections can also be dramatically affected by the design and organization of the overall system. For example, since significant energy is consumed in moving data between main memory and the computational engine, the most power-efficient solutions directly attach DRAM chips to the processor chip without intervening address/control or data redrive circuits, hub chips, or other JEDEC (Joint Electron Devices Engineering Council) [27] standardized devices. In addition, the availability of sufficient I/O pins enables operation of off-chip connections at a modest data rate, which allows for source-terminated interconnects and removes the need for far-end bus termination, thus further reducing power.

#### 1.2.5 Cooling

For several reasons, it is desirable to operate computers such that the junction temperature  $T_i$  of the CMOS transistors is kept in the range of 20°C to 85°C. The reason for the lower bound is to avoid operating electronic components below the dew point (i.e., the temperature at which water would start to condense out of the atmosphere). The reason for the upper bound is twofold: Repeated excursion between low and high temperature (on and off cycles) can cause thermal cycle fatigue of mechanical connections in the chip package. Also, CMOS devices slow and age faster as temperatures increase. Next-generation HPC systems will contain many optical transceivers, and these have an even more limited thermal range. Light output and aging of optical drivers is strongly temperature dependent. For optical transceivers,

it is most desirable to operate at a relatively constant temperature, as close to the dew point as possible.

Within these thermal constraints, we should contemplate how to minimize cost. As large HPC machines are substantial, multimegawatt devices, it is useful to review cooling at the facility level. Unless a large body of water is available nearby, data centers use the atmosphere as a final heat sink. They do so through use of a cooling tower, where return water from the data center is cascaded in a fashion to equilibrate its temperature with the outside air. It is possible in fact for the water temperature leaving a cooling tower and returning to the data center to be several degrees centigrade cooler than the ambient external air. What happens next depends on a choice between air cooling and water cooling. Traditionally, data centers are air cooled, so the water from the cooling tower cycles through a water-to-water heat exchanger, used to cool a closed loop of water, called the chilled water loop. Within the chilled water loop is a water chiller, which reduces the water temperature further, typically to 6°C. At this point, the water pipes need to be insulated to reduce ambient heating of the water and to avoid condensate from the air from forming on the pipes. The chilled water then passes through radiators within computer room air conditioners (CRACs), which use large fans to blow the cooled air beneath a raised floor at a temperature of about 15°C. Alternatively, the air conditioning occurs in larger units within the data center facility, and the cooled air is distributed throughout the data center using air movers and large plenums. Ultimately, the cool air is directed to electronics via local cooling fans within the computer racks. For each watt of power cooled, typically another 0.35 W is used to provide the cooling. In addition, we should consider the cost of purchasing, installing, and servicing the cooling equipment.

A variant of air cooling is hydro-air cooling. Here, the hot air leaving an electronics rack is passed through a radiator, where it is cooled, so that it can be reused for cooling the next rack. Depending on airflow, the water temperature in the radiator, and the heat load, the air temperature leaving the rack could be higher, lower, or the same as the air temperature entering the rack. These systems are advantageous when either the cost of adding additional CRACs is high or if a ready source of water, higher than the 6°C required for CRACs but lower than the exit air temperature, is available for flowing through radiators. Note that the electricity cost of moving air through the CRACs is saved as the fan that directs air through the rack can also drive air through the radiator. A variety of manufacturers makes these radiators, some for individual racks, and some for entire rows of racks.

Their presence and success in the market are appropriate as they can save substantial cost.

An alternative to air cooling is indirect water cooling. It starts in the same manner as air cooling, with a cooling tower and heat exchanger to a closed loop of water. However, this time the closed loop is at 18°C or higher, thus above the dew point of the air in data centers as specified by ASHRAE (American Society of Heating, Refrigerating, and Air-Conditioning Engineers) [28]. This room temperature water enters the computer rack and regulates the temperatures within the rack through contact cooling. Thermal interface materials (TIMs) are used to provide intimate thermal contact between, for example, a copper water pipe and a processor chip or optical transceivers. As it is difficult to cool every component in a rack with indirect water cooling, hybrid systems are used in which most of the heat is exchanged to water and the remaining part to air.

#### **BLUE GENE HARDWARE** 1.3

IBM's Blue Gene series of supercomputers—Blue Gene/L [4], Blue Gene/P [5], and Blue Gene/Q [6, 7]—combine many tens of thousands of lowpower computing nodes of modest performance to yield massive supercomputers that are not only the most power efficient [29], but also the fastest in the world at the time of their introductions in 2004–2011 [30]. Fundamentally based on massive parallelism, Blue Gene systems provide a practical framework within which to discuss the strategies outlined in this chapter. While the Blue Gene systems take some important initial strides toward power efficiency, future systems will likely make more widespread use of the concepts discussed in Section 1.2.

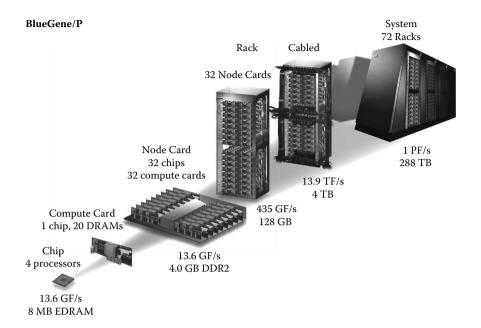

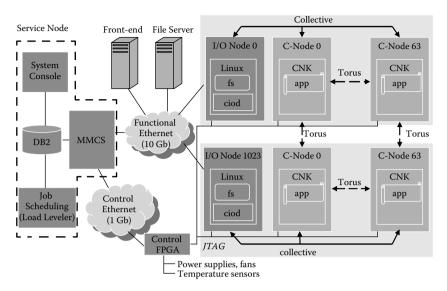

Figure 1.4 shows the Blue Gene/P packaging hierarchy. The packaging hierarchies for Blue Gene/L and /Q are similar. Thirty-two compute cards are packaged onto the next-level board, called the node card. Thirty-two node cards are plugged from both sides into two vertical midplane boards. Thus, 1,024 sockets can be placed and interconnected in a single cabinet. This dense packaging is enabled by the relatively low power of each individual socket. In comparison, a typical rack from other vendors contains about 100 sockets due to power constraints.

The 1,024 compute cards (processor chip with associated DRAM chips) per rack are used as "compute nodes." They are interconnected in a torus topology and run a lightweight operating system (Compute Node Kernel, CNK, described in Section 1.4.1). In addition, a Blue Gene system uses a

FIGURE 1.4 The packaging hierarchy of the Blue Gene/P system. Each chip has four cores. With 32 chips on a node card and 32 node cards per racks, it has 1,024 chips or 4,096 cores in a rack. GF, gigaflops; TF, teraflops; PF, petaflops, EDRAM, embedded DRAM.

smaller set of compute cards as "I/O nodes" to connect to the file system. I/O nodes are placed either in additional slots on the node cards (Blue Gene/L or/P) or in a separate enclosure (Blue Gene/Q). Logically, these I/O nodes are placed "outside" the torus and are connected to the compute nodes by separate links. The I/O nodes run Linux.

#### 1.3.1 Voltage Scaling

The total compute performance in a rack can be simply described as

$$Performance/Rack = Performance/Watt \ x \ Watt/Rack \qquad (1.10)$$

The watt/rack factor is determined by thermal cooling capabilities. We target about 30 kW (kilowatts) for air-cooled racks and about 100 kW for water-cooled racks. Thus, to maximize the performance of a rack, we will need to optimize the performance/watt factor, that is, the power efficiency. We chose the low-frequency, low-power embedded IBM PowerPC 440 core

for Blue Gene/L and the IBM PowerPC 450 core for Blue Gene/P because they had better power efficiency than high-frequency, high-power microprocessors of the time by a factor of about 10, regardless of the manufacturers of the systems. For Blue Gene/Q, we similarly chose the A2 processor, a 64-bit, four-way, multithreaded processor optimized for throughput at relatively low frequency.

The theoretical basis for the superior collective performance of lowpower systems was explained in Section 1.2. Any performance metric, such as FLOPS (floating-point operations per second), MIPS (million instructions per second), or SPEC (Standard Performance Evaluation Corporation) benchmarks is linearly proportional to the chip clock frequency. On the other hand, from Equation 1.1, the power consumption of the *i*th gate on a chip is

$$P_i$$

= Switching Power of Gate  $i$  + Leakage Power of Gate  $i$

=  $\alpha_i C_i V^2 f + I_i V$  (1.11)

In the leakage power term,  $I_i$  is the leakage current multiplied by supply voltage  $V = V_{DD}$ . The leakage power becomes increasingly important as technology dimensions shrink. For Blue Gene/L chips, built in 130nm technology, leakage contributes less than 2% of the system power. For Blue Gene/P, built in 90-nm technology, leakage power is around 8-9% of total power. For Blue Gene/Q, built in 45-nm technology, leakage power is around 14% of total power (in a LINPACK [31] application) but can range up to 20% for chips on the fast end of the manufacturing spread. Operation at the lowest possible voltage for a given technology will minimize the leakage current and thereby leakage power.

In the switching power term,  $C_i$  is the load capacitance of the *i*th gate, and f is the frequency of the fastest on-chip clock. The "switching factor"  $\alpha_i$  expresses that not every gate output will switch on every clock cycle at frequency f. The switching factor  $\alpha_i = 1$  only for the fastest on-chip clock circuits that both charge and discharge a load capacitance every clock cycle at frequency f, transferring a charge  $Q_i = C_i V$  from power supply voltage V to ground. For data circuits, which either charge or discharge a load, at most every clock cycle,  $\alpha_i = 0.5$  or less.

The switching power consumed in a chip then is the sum of the power of all switching gates, expressed as

$$P_{chip} = \Sigma$$

(Switching power of gate  $i$ ) =  $C_{eff} V^2 f$  (1.12)

where the average switching chip capacitance is given by

$$C_{eff} = \Sigma \alpha_i C_i \tag{1.13}$$

It is difficult to predict  $C_{eff}$  accurately because we seldom know the switching factor  $\alpha_i$  of every gate in every cycle. Furthermore,  $\alpha_i$  has a dependence on the instantaneous workload of the circuit. To simplify the discussion, we use an averaged value of Ceff obtained either from direct measurement or from power modeling tools.

As explained in Section 1.2.1, for a given circuit design, the clock frequency f is roughly proportional to the supply voltage V; thus, the power consumed per chip  $P_{chip}$  is proportional to  $V^2 f$  or  $f^3$ . Thus, it is advantageous in terms of power efficiency to run individual processors (of a given design) at the lowest possible voltage for a given technology, and at the corresponding low frequency, and compensate for the lost performance (proportional to f) by increased parallelization—assuming the intended workloads permit such parallelization. This then is a major part of the Blue Gene design philosophy. Of course, the optimal design point also has to consider the complexities of mechanical component counts and sizes, the power required to communicate between the increased number of processors, the failure rate of those processors, the cost of packaging those processors, and so on. The Blue Gene systems are a complex balance of these factors and many more. Table 1.2 shows an overview of the hardware parameters for the three Blue Gene system generations as related to power efficiency.

Blue Gene systems utilize efficient, voltage-scaled processors combined with system-on-a-chip designs that integrate memory controllers, a network router, and an I/O adapter alongside the processor and local cache. The Blue Gene/L, /P, and /Q processor chips, fabricated in 130-nm, 90-nm, and 45-nm processes, respectively, operate at 700, 850, and 1,600 MHzfrequencies well below that of other processors in similar technologies. Table 1.2 also shows that, as Blue Gene designs progressed, the operating voltage progressively decreased below the nominal voltage for the technology, saving on both active and leakage power. As stated previously, the design philosophy is that system-level parallelism will compensate for individual chip performance.

While current Blue Gene systems employ low voltages that are within technology specifications, future designs may leverage subnominal supply voltages to attain greater power efficiency—eventually driving the need for low-voltage device and memory techniques.

TABLE 1.2 Overview of Blue Gene Hardware Parameters Relating to Power Efficiency

|                                                                                    | Blue Gene/L          | Blue Gene/P          | Blue Gene/Q          |

|------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|

| Processor type                                                                     | PPC440               | PPC450               | PPC A2               |

| SIMD FPU per                                                                       | 2 wide               | 2 wide               | 4 wide               |

| processor                                                                          |                      |                      |                      |

| Threads per processor                                                              | 1                    | 1                    | 4                    |

| Processors per chip                                                                | 2                    | 4                    | 16 + 1 + 1           |

| Maximum concurrent threads per chip                                                | 2                    | 4                    | 64 + 4               |

| Chip technology                                                                    | Cu-11 (130 nm)       | Cu-08 (90 nm)        | Cu-45 (45 nm)        |

| Nominal voltage for technology                                                     | 1.5 V                | 1.2 V                | 1.0 V                |

| Blue Gene chip<br>operating<br>voltage under<br>load (for<br>medium-speed<br>chip) | 1.5 V                | 1.1 V                | 0.85 V               |

| Processor                                                                          | 700 MHz              | 850 MHz              | 1600 MHz             |

| frequency                                                                          |                      |                      |                      |

| Chip peak performance                                                              | 5.6 GFLOPS           | 13.6 GFLOPS          | 204.8 GFLOPS         |

| Main memory                                                                        | 0.5- to 1-GB DDR     | 2- to 4-GB DDR2      | 16 GB DDR3           |

| Memory interface bandwidth                                                         | 5.6 GB/s (16 B wide) | 13.6 GB/s (32B wide) | 42.6 GB/s (32B wide) |

| Node power<br>(Chip +<br>DRAMs;<br>Linpack)                                        | ~ 16W                | ~ 23W                | ~ 68W                |

| Node performance                                                                   | $\sim$ 0.28GFLOPS/W  | $\sim$ 0.44GFLOPS/W  | $\sim$ 2.4GFLOPS/W   |

| Nodes per rack                                                                     | 1,024                | 1,024                | 1,024                |

| Rack peak performance                                                              | 5.7 TFLOPS           | 13.9 TFLOPS          | 209.7 TFLOPS         |

| System performance (LINPACK)                                                       | 0.20 GFLOPS/W        | 0.38 GFLOPS/W        | 2.1 GFLOPS/W         |

The bottom row numbers were current entries in the Green500 list June 2012 [29].

# 1.3.2 Low-Power Floating-Point Units

A common method to increase the FLOPS/watt ratio is to integrate multiple floating-point engines on a chip. This concept can be traced back to the early 1970s when vector processors, such as CDC STAR-100 [32] and Cray-1 [33], were introduced. Although not integrated on the same chip at the time, it was recognized that SIMD (single instruction, multiple data) vector processors can increase the performance without a similar increase in power. SIMD floating-point units (FPUs) are also being used extensively in recent HPC systems, such as IBM Cell Engines [34], Intel's Polaris chip [35], and GPUs (graphics processor units) [36].

A modern FPU consumes typically from 0.1 W to a few watts [37, 38], depending on many factors, such as frequency, width of the data path (single precision versus double precision), and so on. However, increasing FPUs from 1 to 8 units incurs a relatively minor increase in the overall chip power. Hence, Blue Gene/L and Blue/P used a two-way SIMD double-precision FPU for each processor core, doubling peak performance and increasing power efficiency at the same time. Blue Gene/Q went further in the same direction and incorporates a four-way SIMD double-precision FPU for each processor core.

Projecting into the future, both voltage-scaling and low-power SIMD FPUs will continue to be the foundation of power-efficient supercomputer designs.

# 1.3.3 Power Delivery

In a massive parallel system, generating, monitoring, and preserving the requisite supply voltages can be challenging—due to the sheer number of voltages required and the stringent requirements on supply robustness and redundancy. With increased parallelism and voltage scaling, these issues will become more severe in future-generation systems.

To facilitate efficiency in chip-to-chip communications and to enable cycle-reproducible operation, a single system clock is distributed to all compute nodes in a Blue Gene system. Since each processor chip must run at the same frequency, tailored supply voltages are used to minimize power in the presence of process variations. In manufacturing, chips are speed sorted into groups. The 32-way node cards are populated homogeneously with chips of a given speed sort bin, and the power supplies on the node card are adjusted—with the fastest chips (which also have the most leakage current)

running at a lower voltage and the slowest chips running at a higher voltage. This approach minimizes both active and leakage power.

With a multitude of supplies operating at high current levels and energy densities, redundancy, supply stability, and infrared (IR) with resistive losses must be carefully addressed. To ensure high system reliability, supply voltages are provided by distributed point-of-load converters with N+1or N + 2 redundancy. While a supply failure may create a large transient response, the frequent near-instantaneous changes of up to 40% in processor power due to synchronous clocks and power-gating techniques also create large voltage transients. The power converter loop response and recovery from a supply failure must be fast enough so that the voltage droop does not fall below the minimum voltage required to run the processor. To ensure this, the nominal voltage is raised high enough to cover the worstcase voltage droop and thus adds to the nominal power dissipation. Power planes on the circuit cards are designed to minimize these droops and match the voltage delivered to each processor chip. Processor nodes far from the power supply have additional conduction paths in other circuit card layers to reduce resistance while parallel connections may be removed from other nodes. As a result, supply equipotentials are created at each processor chip location. The number of power planes on a circuit card is fixed, however, such that as extra power supply voltages are added (as needed for DRAM and I/O), distribution losses inevitably worsen.

On Blue Gene/Q, the final stage of DC-DC voltage conversion is performed directly on the system planar. In future systems, as discussed in Section 1.2.3, the final stage of DC-DC voltage conversion will ideally be performed on the processor chip itself. By delivering higher voltages closer to the chip, supply stability and resistive losses can be improved, which will be especially important as operating voltages are further scaled down. In addition, local voltage generation and regulation could significantly simplify the power delivery system by reducing the number of supplies needed.

### 1.3.4 **Off-Chip Connections**

As discussed in Section 1.2.4, the power associated with moving data between processor and memory is minimized if the memory controller is located directly on the processor chip. In Blue Gene systems, each processor chip contains a wide interface (16B wide for Blue Gene/L; 32B wide for Blue Gene/P and /Q) to directly attached memory (see Table 1.2).

Source-terminated I/O cells that are impedance matched to the transmission lines between the processor and DRAM eliminate the need for other data line termination. The power dissipated in these lines follows Equation 1.9, where the capacitance is minimized by placing memory immediately adjacent to the processor chip. Using variable-voltage I/O cells and corresponding power supplies, low-voltage memory can be introduced as it becomes available.

Going forward, processor-to-memory bus frequencies will increase. Thus, the power dissipated in the connections between the processor and external memory will increase unless the interconnect capacitance can be reduced to compensate for increasing bus frequencies. By utilizing high I/O count DRAM stacks, based on through-silicon vias or other high-wiring-density interconnect media, large amounts of external DRAM can be placed adjacent to the processor with greatly reduced wiring path lengths.

The longest off-chip connections in a Blue Gene system are used for communication between racks. In Blue Gene/L and /P these links, which can be up to 8 m in length, are managed by electrical cables using differential signaling at up to 3.4 Gb/s (gigabits per second). In Blue Gene/Q, the rack-to-rack communication links are optical fiber connections. In optical connections, attenuation is substantially less than in electrical connections, which means that links of up to 100 m will operate with little or no more power than links of a few meters—a characteristic that may lead to new system design paradigms.

### 1.3.5 Cooling

Blue Gene/L is entirely air cooled. At 25 kW/rack, it is a relatively highpower machine but still coolable in most data centers without difficulty. In traditional data centers, the airflow enters the machine room proper through perforations in the raised floor, is typically pulled through electronics racks from a "cold aisle" in front of a row of racks to a "hot aisle" in back of a row of racks, and then somehow makes its way back to the CRAC units on the perimeter of the raised floor or, via exhaust vents, to a facility-level air conditioning plant. Indeed, many data centers must leave vast expanses of valuable machine room floor unoccupied to allow enough perforations for the volume of air required for high-power HPC machines.

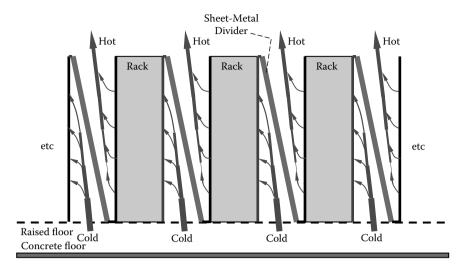

Blue Gene/L improves on the efficiency of the airflow. As shown in Figure 1.5, cold air is drawn directly from the raised floor into a tapered side

FIGURE 1.5 Airflow through a row of Blue Gene/L or /P racks, showing complementary tapered plenums.

plenum. A wall of fans pulls the air across the rack and exhausts into a second plenum, which directs the warm air to the ceiling. A ceiling plenum returns the air to the air conditioners. Only the bulk power supplies on top of the rack are cooled with air in the machine room proper, and even this air is drawn from the aisle and directed upward, permitting all aisles to be "cold aisles." Thus, the Blue Gene/L solution allows a compact design, with aisle width limited only by the needs of people access, further reducing cost. Further, the unique side-to-side airflow permits a midplane design without air perforations, so that a maximum number of circuit cards can be connected together without electrical cables, thus reducing power and cost.

Blue Gene/P increased the rack power to 32 kW, which is more challenging for air cooling. However, the side-to-side airflow of Blue Gene allows the straightforward introduction of hydro-air cooling, in the form of radiators between racks. These radiators have sufficient cooling capability to cool the air leaving a rack back to its entrance air temperature. A cost analysis comparing air cooling with CRACs to hydro-air cooling for Blue Gene/P, including estimates for equipment purchase as well as electricity cost of \$0.10/kWh, resulted in about \$7,500 savings per rack over a 5-year lifetime. This analysis includes the purchase and power of a commercial water conditioner to raise the chilled water temperature to above the dew point before entering the rack radiator. If a ready supply of 18°C closed-loop water is available, the cost savings more than doubles. The largest installed

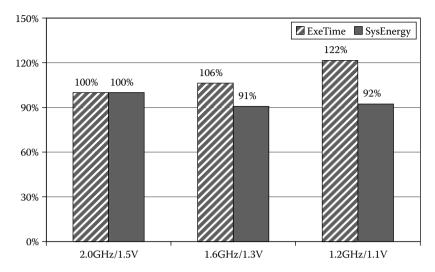

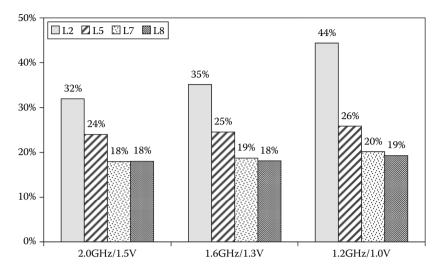

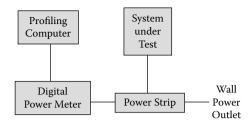

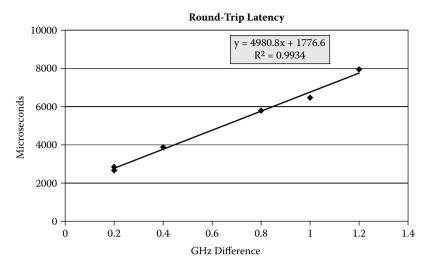

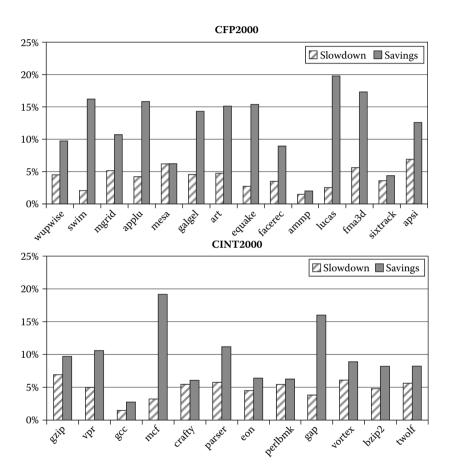

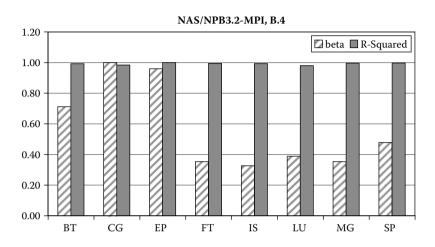

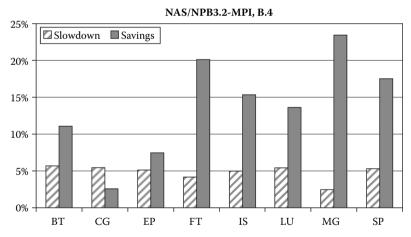

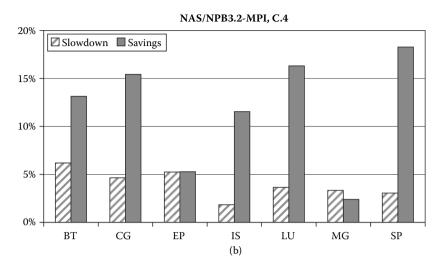

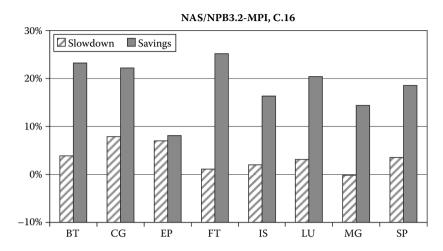

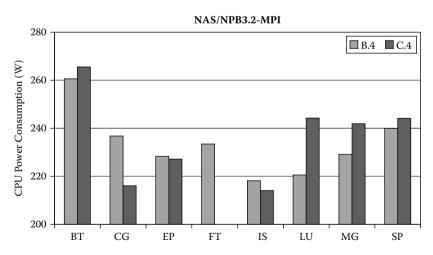

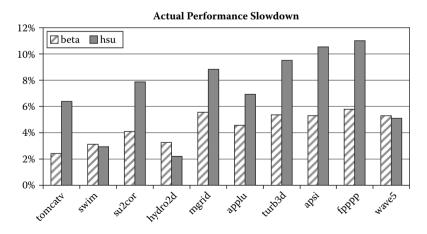

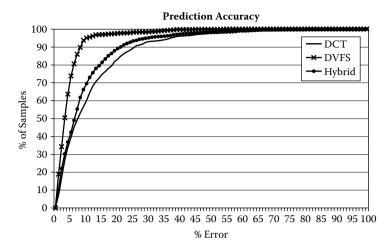

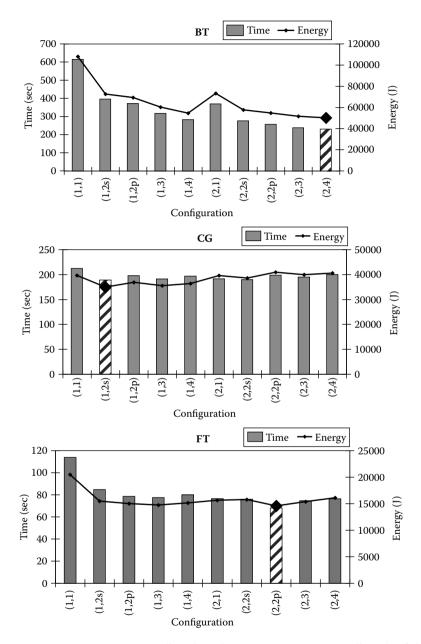

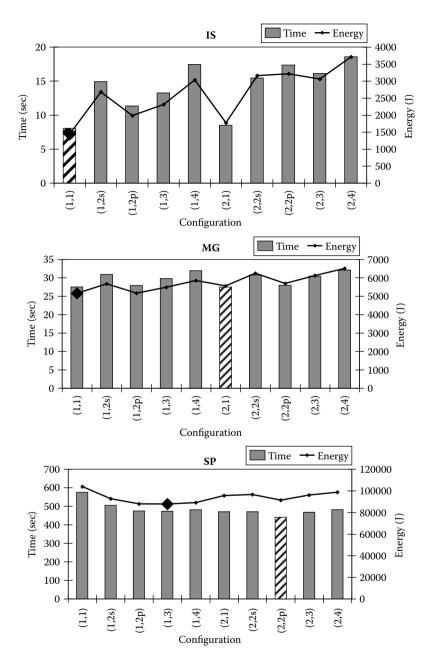

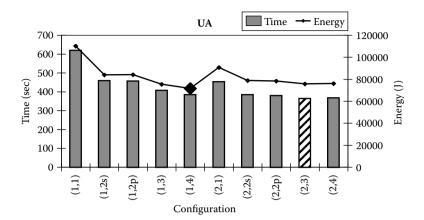

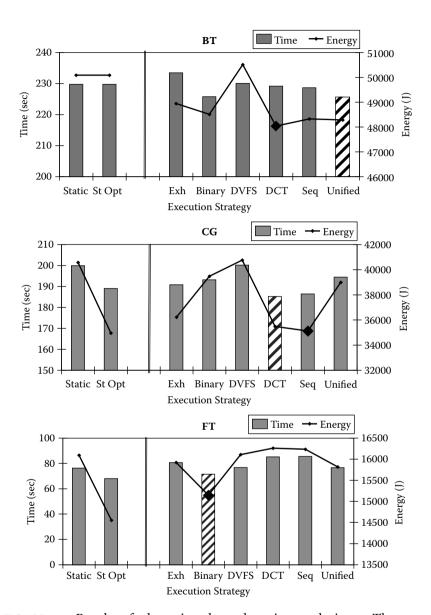

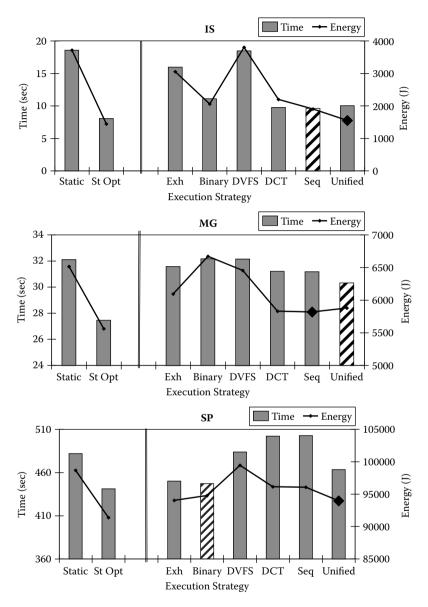

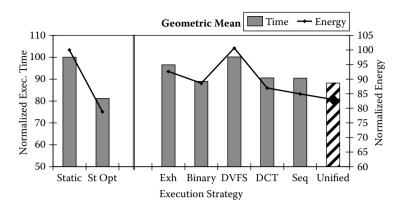

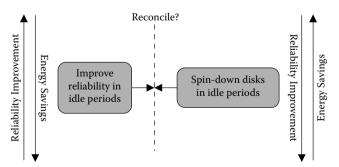

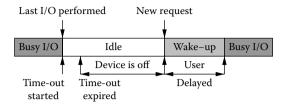

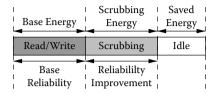

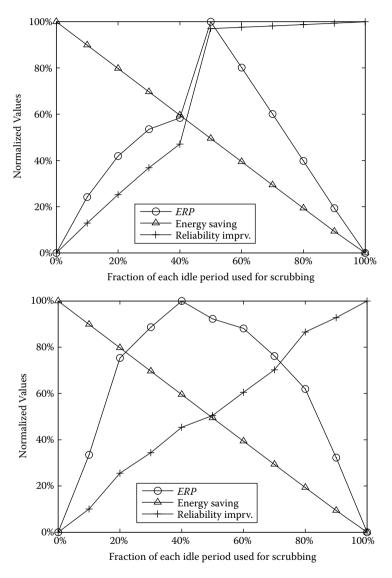

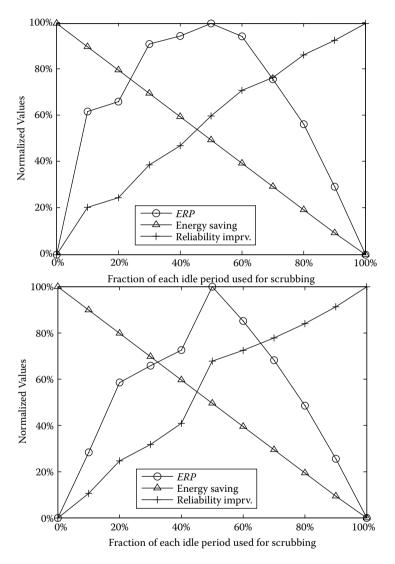

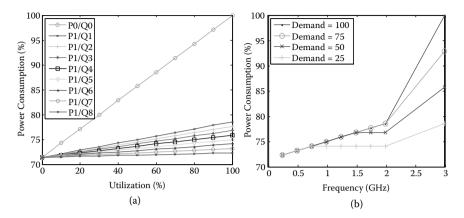

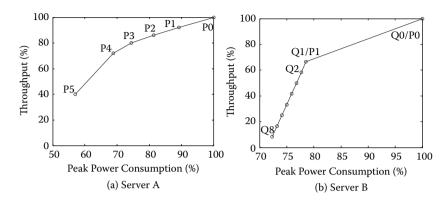

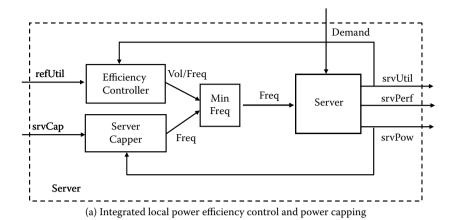

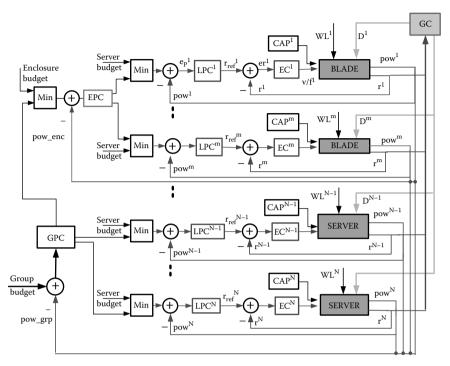

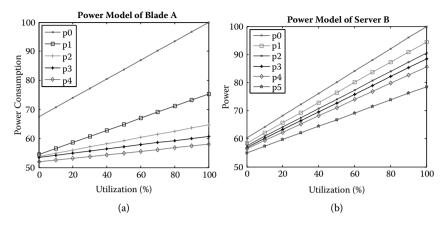

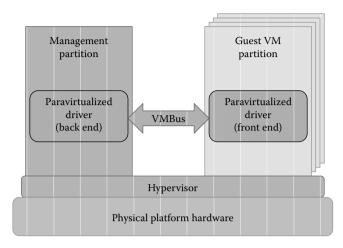

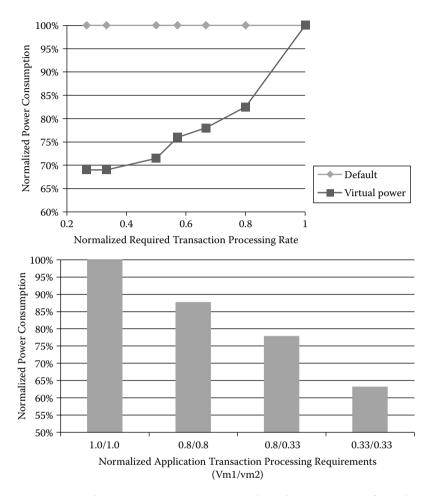

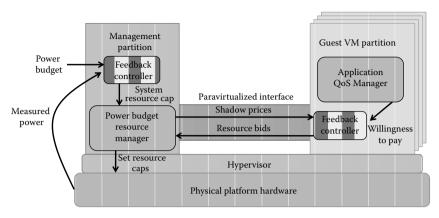

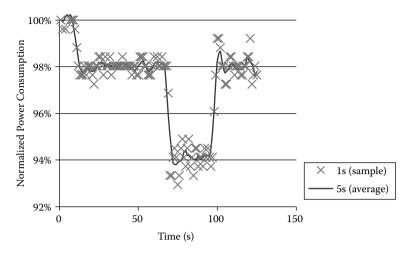

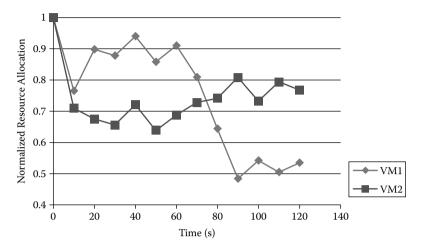

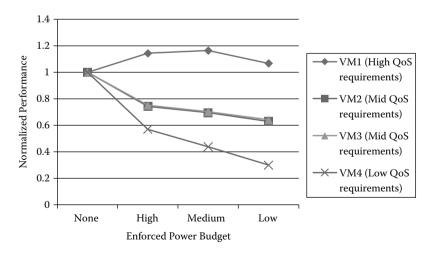

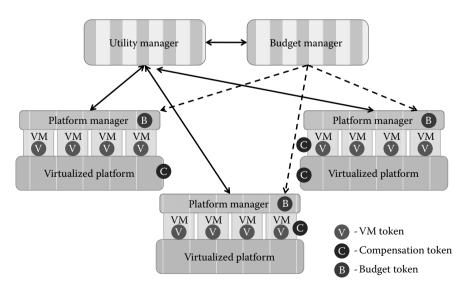

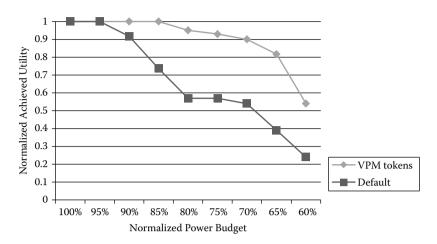

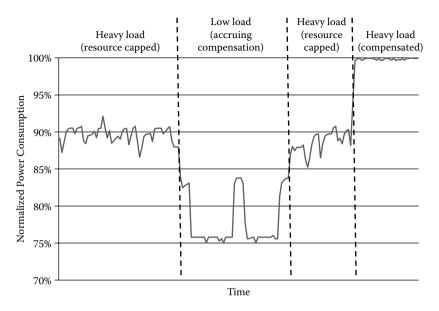

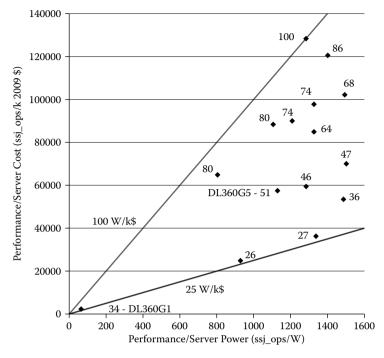

Blue Gene/P system, a 72-rack, 1-PetaFLOPS machine in Jülich, Germany, is cooled via the hydro-air technique and a facility-level water conditioning unit.